A computer program has only two ways to determine the conditions that exist in internal and external circuits. One method uses software instructions that jump on the states of flags and port pins. The second responds to hardware signals. called interrupts. that force the program to call a sub-routine. Software techniques use up processor time that could be devoted to other tasks; interrupts take processor time only when action by the program is needed. Most applications of microcontrollers involve responding to events quickly enough to control the environment that generates the events (generically termed "real-

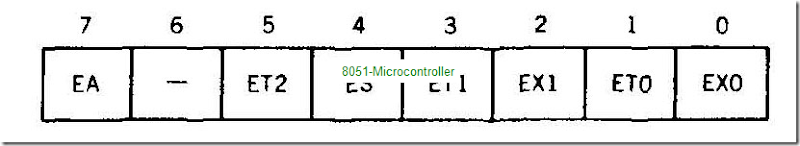

FIGURE 17 IE and IP Function Registers

| Bit | symbol | Function |

| 7 | EA | Enable interrupts bit. Cleared to 0 by program to disable all interrupts; set to 1 to permit individual interrupts to be enabled by their enable bits. |

| 6 | - | Not implemented. |

| 5 | ET2 | Reserved for future use. |

| 4 | ES | Enable serial port interrupt. Set to 1 by program to enable serial port interrupt; cleared to 0 to disable serial port interrupt. |

| 3 | ET1 | Enable timer 1 overflow interrupt. Set to 1 by program to enable timer 1 overflow interrupt; cleared to 0 to disable timer 1 overflow interrupt. |

| 2 | EX1 | Enable external interrupt 1. Set to 1 by program to enable (INT1)' interrupt; cleared to 0 to disable (INT1)' interrupt. |

| 1 | ET0 | Enable timer 0 overflow interrupt. Set to 1 by program to enable timer 0 overflow interrupt; cleared to 0 to disable timer 0 overflow interrupt. |

| 0 | EX0 | Enable external interrupt 0 . Set to 1 by program to enable (INTO)' interrupt; cleared to 0 to disable (INTO)' interrupt. |

Bit addressable as IE.0 to IE.7

THE INTERRUPT PRIORITY (IP) SPECIAL FUNCTION REGISTER

| Bit | symbol | Function |

| 7 | - | Not implemented. |

| 6 | - | Not implemented. |

| 5 | PT2 | Reserved for future use. |

| 4 | PS | Priority of external interrupt 1. Set/cleared by program. |

| 3 | PT1 | Priority of timer 1 overflow interrupt. Set/cleared by program. |

| 2 | PX1 | Priority of serial port interrupt. Set/cleared by program. |

| 1 | PT0 | Priority of timer 0 overflow interrupt. Set/cleared by program |

| 0 | PX0 | Priority of external interrupt o. Set/cleared by program. |

Note: Priority may be 1 (highest) or 0 (lowest)

Bit addressable as IP.O to IP.7

time programming"). Interrupts are often the only way in which real-time programming can be done successfully.

Interrupts may be generated by internal chip operations or provided by external sources. Any interrupt can cause the 8051 to perform a hardware call to an interrupt-handling subroutine that is located at a predetermined (by the 8051 designers) absolute address in program memory.

Five interrupts are provided in the 8051 . Three of these are generated automatically by internal operations: timer flag 0, timer flag 1, and the serial port interrupt (RI or TI). Two interrupts are triggered by external signals provided by circuitry that is connected to pins (INT0)' and (INT1)' (port pins P3.2 and P3.3).

All interrupt functions are under the control of the program. The programmer is able to alter control bits in the interrupt enable register (IE), the interrupt priority register (IP), and the timer control register (TCON). The program can block all or any combination of the interrupts from acting on the program by suitably setting or clearing bits in these registers. The IE and IP registers are shown in Figure 17.

After the interrupt has been handled by the interrupt subroutine, which is placed by the programmer at the interrupt location in program memory, the interrupted program must resume operation at the instruction where the interrupt took place. Program resumption is done by storing the interrupted PC address on the stack in RAM before changing the PC to the interrupt address in ROM. The PC address will be restored from the stack after an RETI instruction is executed at the end of the interrupt subroutine.

When a timer/counter overflows, the corresponding timer flag, TF0 or TF1, is set to 1. The flag is cleared to 0 when the resulting interrupt generates a program call to the appropriate timer subroutine in memory.

If a data byte is received, an interrupt bit, RI, is set to 1 in the SCON register. When a data byte has been transmitted an interrupt bit, TI, is set in SCON. These are ORed together to provide a single interrupt to the processor: the serial port interrupt. These bits are not cleared when the interrupt-generated program call is made by the processor. The program that handles serial data communication must reset RI or TI to 0 to enable the next data communication operation.

Pins (INT0)' and (INT1)' are used by external circuitry. Inputs on these pins can set the interrupt flags lE0 and IE1 in the TCON register to 1 by two different methods. The IEX flags may be set when the (INTX)' pin signal reaches a low level, or the flags may be set when a high-to-low transition takes place on the (INTX)' pin. Bits ITO and ITI in TCON program the (INTX)' pins for low-level interrupt when set to 0 and program the (INTX)' pins for transition interrupt when set to 1 .

Flags IEX will be reset when a transition-generated interrupt is accepted by the processor and the interrupt subroutine is accessed. It is the responsibility of the system designer and programmer to reset any level-generated external interrupts when they are serviced by the program. The external circuit must remove the low level before an RET1 is executed. Failure to remove the low will result in an immediate interrupt after RET1 , from the same source.

A reset can be considered to be the ultimate interrupt because the program may not block the action of the voltage on the RST pin. This type of interrupt is often called "non-maskable," since no combination of bits in any register can stop, or mask the reset action. Unlike other interrupts, the PC is not stored for later program resumption; a reset is an absolute command to jump to program address 0000h and commence running from there.

Whenever a high level is applied to the RST pin, the 8051 enters a reset condition.

After the RST pin is brought low, the internal registers will have the values shown in the following table:

| REGISTER | VALUE(HEX) |

| PC | 0000 |

| DPTR | 0000 |

| A | 00 |

| B | 00 |

| SP | 07 |

| PSW | 00 |

| P0-3 | FF |

| IP | XXX00000b |

| IE | 0XX00000b |

| TCON | 00 |

| TMOD | 00 |

| TH0 | 00 |

| TL0 | 00 |

| THl | 00 |

| TL1 | 00 |

| SCON | 00 |

| SBUF | XX |

| PCON | 0XXXXXXXb |

Internal RAM is not changed by a reset; however, the states of the internal RAM when power is first applied to the 8051 are random. Register bank 0 is selected upon reset as all hits in PSW are 0.

The program must be able, at critical times, to inhibit the action of some or all of the interrupts so that crucial operations can be finished. The IE register holds the programmable bits that can enable or disable all the interrupts as a group, or if the group is enabled, each individual interrupt source can be enabled or disabled.

Often, it is desirable to be able to set priorities among competing interrupts that may conceivably occur simultaneously. The IP register bits may be set by the program to assign priorities among the various interrupt sources so that more important interrupts can be serviced first should two or more interrupts occur at the same time.

Bits in the EI register are set to 1 if the corresponding interrupt source is to be enabled and set to 0 to disable the interrupt source. Bit EA is a master, or "global," bit that can enable or disable all of the interrupts.

Register IP bits determine if any interrupt is to have a high or low priority. Bits set to I give the accompanying interrupt a high priority while a 0 assigns a low priority. Interrupts with a high priority can interrupt another interrupt with a lower priority; the low priority interrupt continues after the higher is finished.

If two interrupts with the same priority occur at the same time, then they have the following ranking:

I. IE0

2. TF0

3. IE1

4. TF1

S. Serial = RI OR TI

The serial interrupt could be given the highest priority by setting the PS bit in IP to I, and all others to 0.

Each interrupt source causes the program to do a hardware call to one of the dedicated addresses in program memory. It is the responsibility of the programmer to place a routine at the address that will service the interrupt.

The interrupt saves the PC of the program, which is running at the time the interrupt is serviced on the stack in internal RAM. A call is then done to the appropriate memory location. These locations are shown in the following table:

| INTERRUPT | ADDRESS(HEX) |

| IE0 | 0003 |

| TF0 | 000B |

| IE1 | 0013 |

| TF1 | 001B |

| SERIAL | 0023 |

A RETI instruction at the end of the routine restores the PC to its place in the interrupted program and resets the interrupt logic so that another interrupt can be serviced. Interrupts that occur but are ignored due to any blocking condition (IE bit not set or a higher priority interrupt already in process) must persist until they are serviced, or they will be lost. This requirement applies primarily to the level-activated (INTX)' interrupts.

When any interrupt flag is set to I by any means, an interrupt is generated unless blocked. This means that the program itself can cause interrupts of any kind to be generated simply by setting the desired interrupt flag to I using a program instruction.

Labels: 8051 architecture